# ネットワーク通信改善のための高度なパッケージング

Amkor Technology, Inc. Product Marketing and Business Development 担当 Sr Director Vik Chaudhry、および Advanced Package & Technology Integration 担当 VP Mike Kelly

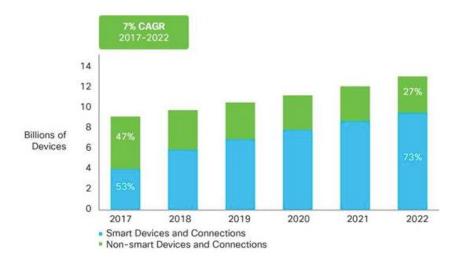

データに関する世界需要は日に日に高まっています。Ring などのセキュリティカメラ、Amazon や Google のスマートスピーカー、Roku や Apple Plus などのストリーミングデバイスやサービスなど、身の回りのスマートデバイスが増えれば増えるほど、データ通信量も飛躍的に増えていきます。ある推定では、100億台のインタネット接続(IoT)デバイスがあり(図1参照)、30 エクサバイト(EB)(30\*10<sup>18</sup>バイト)のデータを毎月伝送しています。そのデータの 70%は、現在、ストリーミングビデオの形で提供されています。このデータのうちビデオコンテンツは、2022年には80%まで増加すると予想されています。同時に、データ伝送速度も増加し、今後10年以内には1テラビット/秒(Tbps)を超えると予想されています[1]。

図 1: IoT デバイスは現在の 100 億個から 2022 年には 120 億個に増加すると言われている 出典: Cisco VNI Mobile, 2019

この大規模なデータ伝送は、ハイパースケールデータセンターに多大な負担をかけます。お客様がデータ伝送を行う際に、データセンターは迅速に対応し、情報を遅延なく適時に送る必要

があります。つまり、データセンターのネットワーキングデバイスは、大量のデータをより高速に処理する必要があるのです。

仮想化と SDN(Software Defined Networking)により、ハイパースケールデータセンター内に複数レイヤーのスイッチングができることになりました。データは、お客様に返送される前に、データセンター内のトップオブラック(TOR)、リーフ、スパインの各スイッチ間を移動する場合があります。古いデータセンターでは、TOR をつなぎ合わせた North-South トラフィックが一般的でした。一方、ハイパースケールデータセンターでは、 East-West トラフィックが多くなった SDN や仮想化が採用されています。データは多くのサーバーに分割されるため、リーフスイッチやスパインスイッチの必要性が生じます。

## Integrated Packaging Solutions (統合パッケージングソリューション)

高性能スイッチの性能を向上させるために、異なるビルディングブロックの距離を短くする傾向が強まっています。従来は、ビルディングブロックをすべてシステム・オン・チップ (SoC) 上に統合していましたが、そのアプローチには2つの問題があります。1つは、そのような SoC は大きくなりすぎ、レチクルサイズよりも大きくなってしまうことです。7 nm のような高度プロセスノードでは、このようなデバイスのコストは高すぎる場合があります。もう一つの問題は、チップが大きくなればなるほど、生産量が落ちてしまい、さらにコストがかかってしまいます。

このような状況に対処するため、複数の小さなチップを単一パッケージに統合するチップレットアプローチに注目が集まっています。小さなプロセスノードに必要なロジック部分だけを残し、他のアナログやシリアライザ/デシリアライザ (SerDes)機能、メモリなどは、より大きなプロセスノードのチップで設計、処理されます。同一パッケージ内では、異なるチップが互いに近接しています。チップレットアプローチは、全体的なコストを削減し、個別の歩留まりを向上させ、よりよいパフォーマンスを実現します。お客様の中には、ロジックチップを2つに分割して「ダイ・パーティショニング」にすることも検討されています。これにより、大型ロジックチップの歩留まりがさらに向上します。

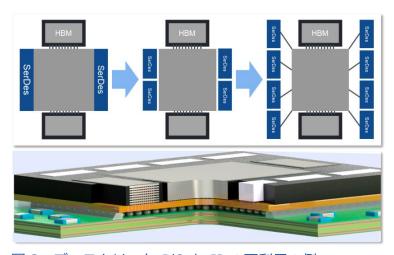

図 2 は、システム設計者がソリューションを構築する際の一例です。SerDes と高帯域幅メモリ (HBM) を搭載した特定用途向け集積回路 (ASIC) は、総合的なソリューションを提供します。これらの設計における HBM の数は増加しており、1 つのパッケージに 6~8 個の HBM スタックを検討しているものもあります。ディスクリート I/O チップが使われる理由は、SerDes の I/O チップはプロセスノードに対する拡張がうまくいかず、従来から使われている安価なシリコンノードのままにできる可能性があるからです。これにより、同じチップを他の製品に使用することができ、単一の SOC チップで可能な範囲よりも I/O の総数を増やすことができるので、知的財産権の再利用が可能になります。

図 2: ディスクリート I/O と IP の再利用の例

異なる種類の半導体技術をパッケージレベルインテグレーションや、ヘテロジニアスインテグレーションに対応する方法は数多くあります。1 つは、パッケージサブストレートに異なるチップを取り付けたマルチチップモジュール(MCM)のアプローチです。2 つ目のアプローチは、高密度モジュールを使用するもので、例として 2.5D 構造があり、シリコンインターポーザを使用して異なるチップ同士をつなぎます。また、高密度ファンアウト(HDFO)技術を用いて、Cu と有機誘電体でインターポーザを製造する方法もあります。これにより、高価なインターポーザのチップが不要になります。次いで、HDFO サブシステムをパッケージサブストレート上に配置することができます。Amkor では、このような構造を S-SWIFT®(Substrate Silicon Wafer Integration Fan-out Technology)パッケージングと呼んでいます。

機能が追加された ASIC チップは、レチクルサイズに近づいているようです。ディスクリート HBM や SerDes チップを集積したパッケージサブストレートは、現在、75×75 mm や 85×85 mm 近づいているものもあり、高密度モジュールでは 40×50mm に近づいています。将来的には、シリコンフォトニクスを搭載し、一辺が 100 mm の大きさになるようなパッケージも出てきます。

50 Gbps 超のデータレートでは、ナイキスト周波数を下げてチャネルロスを低減するために、4つのレベルを持つパルス振幅変調(PAM4)が使用されます。SEMI のヘテロジニアス集積のロードマップ 2019 年度版[2]によると、PAM に伴う信号対雑音比(SNR)の低下、電力の増加、クロストーク問題を回避するためには、「インターコネクトの距離を短くするために、デバイスを互いに近づけることができる高集積システム」が長期的なソリューションとなります。

### Advanced Multi-layer Packaging (アドバンストマルチレイヤーパッケージング)

SWIFT パッケージングは、Amkor が 2013 年に開発した高密度ファンアウト(HDFO)技術です。この設計技術により、RDL 技術を併用して複数のチップを組み立てることができ、ますます小型化と狭小化が進んでいます。これはダイラストプロセスであるため、ファンアウト層を完全に製造した後、AOI を使用してチップ搭載可能と判断した箇所にのみチップが搭載されます。これは歩留まりの向上に貢献しています。小さなジオメトリを持つ SWIFT デザインは、優れたパフォーマンスを低コストで提供します。すでにモバイルアプリケーションに広く利用されていますが、ネットワーキングやハイパフォーマンス・コンピューティング(HPC)のアプリケーションにも利用できます。この高度パッケージング設計アプローチを推進する主要因としては次のものがあります:

- ▶ フォームファクタ(仕様や規格)の縮小

- シグナルインテグリティ(デジタル信号の品質)の強化

- 優れたインピーダンスマッチング

- 最適な電力配分

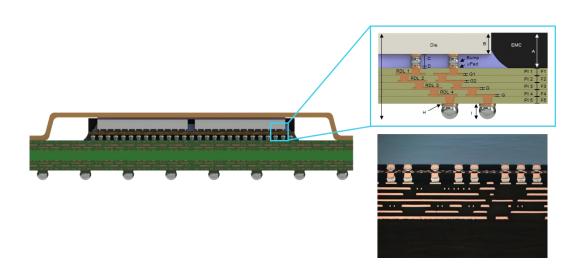

図 3 は、サブストレート SWIFT または S-SWIFT (HDFO on substrate) 構造の代表的な構造を示しています。通常、S-SWIFT デザインは、4 RDL (RDL ファースト、チップラスト) 構造物を持ちます。レイヤー1 とレイヤー3 は信号配線に使用され、レイヤー2 は接地に使用されます。レイヤー4 は、プレーンとしても Cu ピラー (CuP) としても使用することができます。

S-SWIFT パッケージングは、30~80 µm(代表値)のバンプピッチに対応し、RLD レイヤー 1~4 のライン/スペーシングは 2/2µm となります。いくつかのお客様が、ASIC とチップレット(SerDes、HBM その他)のインテグレーションに SWIFT 技術を使うことを検討しています。優れた電気特性と柔軟性を持つ SWIFT 技術は、ダイ・パーティション・モジュールにも適しています。図 3 は、複数のレイヤーの相互接続(インターコネクト)を示しています。

図 3: S-SWIFT® パッケージングは、多層の Cu と有機誘電体 RDL を採用

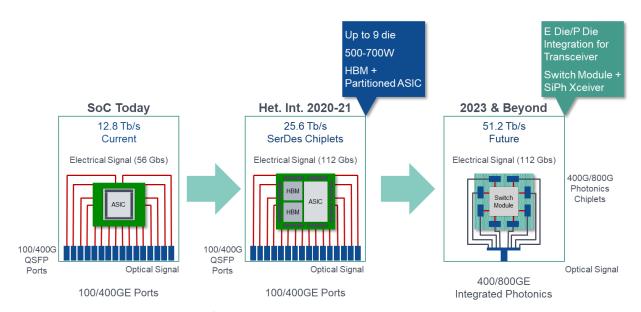

ネットワーキングデバイスのロードマップを見ると、ヘテロジニアス・パッケージング技術は さまざまな形態で使われているようです(図 4 参照)。現在のネットワーキングスイッチは、 14 nm または 7 nm プロセスノードのモノリシック SoC で、通常 12.8 テラビット/秒 (Tbps) の容量に対応しています。今後はより小さなプロセスノードに移行し、25.6Tbps の 容量に対応することを検討しています。これはヘテロジニアスデバイス集積が効果を生み出す

アーキテクチャです。チップの大型化に伴い、ASIC のロジック機能を I/O から分離することが大きな課題となっています。システムメモリの帯域幅を向上させるために、同一パッケージ内で ASIC と統合される HBM も増えています。SWIFT パッケージングは、ASIC、SerDes、HBM を統合することができます。Amkor は、そう遠くない将来、シリコンフォトニクスもこのソリューションを構成するようになると考えています。

図 4: スイッチのロードマップの進展は、統合されたシリコンフォトニクスのソリューション につながる

短期的には、お客様は利用可能なツールを使ってハイパフォーマンス・コンピューティングのソリューションをコスト面で最適化したいと考えています。5 nm および 3 nm ノードのウェハが高コストであることから、大型 ASIC のチップを 2 つのパーツに分割し、場合によってはHDFO や RDL モジュールに HBM を付随させる必要があります。SerDes の I/O ドライバーは、他のロジックのようにジオメトリのプロセスを小さくする必要がないため、チップレット形態になります。実装されるソリューションは、FCBGA(Flip Chip Ball Grid Array)パッケージで、超高速シグナリング用に低誘電率(Df)と低誘電(Dk)の特性を持つ材料を使用しています。

シリコンフォトニクス技術は、スイッチ市場に急速に浸透しています。シリコンフォトニクス の構成要素は、光の信号を受け取り、それを電気信号に変換したり、逆にデータ処理したりす ることができます。課題としては、このソリューションのための共通のアーキテクチャがないことが挙げられます。お客様によって、これらの技術を統合する方法は異なっています。ヘテロジニアスデバイス集積、Optical アラインメント、大量生産は、今でも業界にとって大きなハードルの一つです。

#### アドバンストパッケージ用のテクノロジーツールボックス

ネットワーキングやハイパフォーマンス・コンピューティング(HPC)アプリケーションなど、大規模なヘテロジニアスソリューションに関連する障害を解決するために、Amkor はツールキットを開発しました。Amkor のツールボックスには次が含まれます:

- 1. 最大で片側 85 mm の大型パッケージサイズ

- 2. 複数のチップのアセンブリとテスト性能

- 3. 高度サーマルインターフェイス材(TIM)

- 4. 高性能を実現する S-SWIFT パッケージング

#### 電気特性シミュレーション

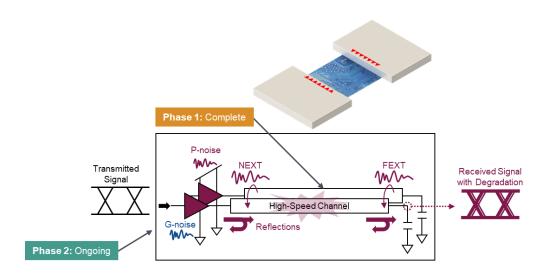

112 Gbps の速度に対応する SerDes や、パッケージ内で複数のチップが相互に通信するため、正確なパッケージモデルで電気シミュレーションを行うことが重要になります。これらのシミュレーションでは、配電ネットワークだけでなく、配線経路も考慮することが推奨されます。Amkor は、配線経路を正確にモデル化する能力を持ち、予想される電源ノイズもモデル化して、パッケージがシステム性能に与える影響をお客様に理解していただけるようにしました。図 5 は、Amkor がシミュレーション目的のために使用しているセットアップを示しています。シミュレーションには、配線経路だけでなく、地面や電源ノイズも含まれています。

図 5:配電ネットワーク(PDN)の伝送とシグナルインテグリティは、高度パッケージングの重要な側面です。

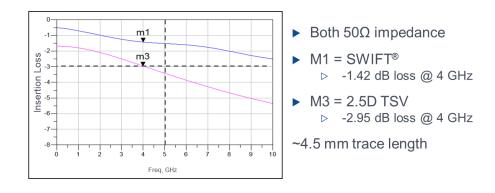

図6の表示で、S-SWIFT パッケージングは、インターポーザ内の2.5D 信号配線と比較して、はるかに低い挿入損失を示しています。オフチップ信号シリコン貫通電極(TSV)パッケージング。2.5D 構造であれば、お客様は4GHz 付近で3dB の信号損失を期待できます。SWIFT 構造は、3dB の挿入損失を記録する前に10GHz を超えることができます。これは、アプリケーションの設計者がSWIFT 構造物に関して期待できるマージンを示しています。

図 6: フェーズ 1 のテストでは、S-SWIFT® パッケージは、特に高周波において、2.5D TSV に比べてチップからチップへ送られる信号について挿入損失を大幅に低減する

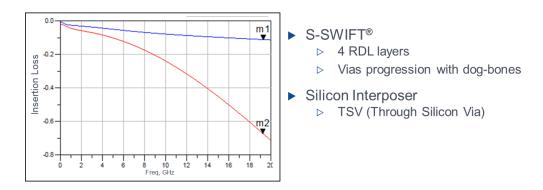

図 7 に示すように、SWIFT 構造では、TSV 構造に比べて損失が少ないです。これらはオフパッケージによる信号です。

図 7: S-SWIFT® パッケージングは、2.5D TSV - オフパッケージよりもはるかに低い損失を 実現する

より高速でより多くの機能を持つため、電力消費の課題に対応しなければなりません。500W の消費電力を改善する方法はあります。お客様には、ソリューションをリッド付きにしたいのか、スティフナーリング付きのベアチップにしたいのかを選んでいただきます。シリコンとリッドの間、またはリッドとヒートシンクの間にある TIM は、パッケージから放熱するために重要な役割を果たしています。リッドの厚さと TIM の正しい選択をするため、低コストのインジウム冶金 TIM の量産化を含むいくつかの開発が進行中です。

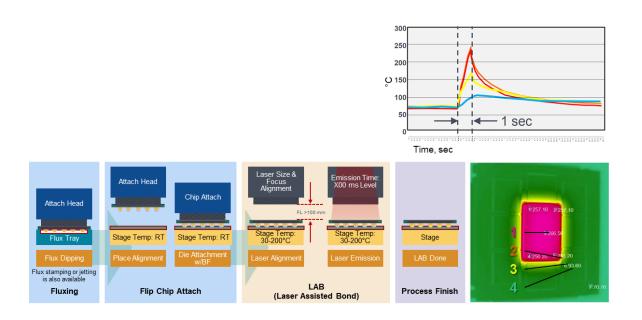

大型ボディのヘテロジニアスパッケージに関するもう一つの課題が、反りの問題です。反りは避けられませんが、それを制限することでパッケージの歩留まりを改善する方法があります。この分野で役立っているのが、レーザーアシストボンディング(LAB)という技術です。LAB 技術では、レーザーを使ってチップを局所的に加熱し、サブストレートにはんだ付けしています。LAB のメリットをいくつか挙げてみましょう:

- ▶ バルク加熱を避け、IC とサブストレート間の熱膨張係数(CTE)の不一致を最小限に抑えることができます

- ▶ 大型で薄いサブストレートでも優れた反りの制御を発揮します

- 側壁のはんだのウィッキングが少なくなります

図8は、LAB 技術を使用する際の様々な側面を示しています。チップを局所的に加熱することで、サブストレートの拡張と縮小が最小限に抑えられるため、バンプや低 k レイヤーのストレスレベルを下げることができます。

図 8: HDFO パッケージの様々な箇所におけるレーザーアシストボンディングのプロファイル

特に高速ネットワーク用のアドバンストパッケージングの一環として、Amkor は設計におけるチップレットの数を増やし、また S-SWIFT パッケージのサイズを増やすことにも継続的に取り組んでいます。HBM が HBM2 から HBM2E へ、また間もなく HBM3 へと移行する中、Amkor はお客様と緊密に連携しながら、この移行に不可欠な役割を果たそうとしています。そのほかの活動として、モジュールレベルの新製品で組み込みバイパスキャップを使用する計画もあります。また、超高密度インターコネクト用に 1/1 の L/S を提供する S-Connect 技術も検討しています。

Amkorでは、ヘテロジニアスデバイス集積が最先端パッケージング設計の基礎となっています。お客様が今日のネットワークシステムの性能需要の増加に対応できるよう、すでに様々な技術が提供されています。今後の開発では、信号伝送、ワット損、長期信頼性などの性能をさらに向上させるとともに、将来のネットワーク用のコスト効率の高いパッケージングソリューションのニーズに対応していきます。

## 参考資料

[1] Cisco Visual Networking Index (VNI) Global and Americas/EMEAR Mobile Data Traffic Forecast、2017-2022

[2] Heterogeneous Integration Roadmap, 2019 Edition、Chapter 2: High Performance Computing and Data Centers, IEEE

SWIFT は、Amkor Technology, Inc. の登録商標です

2020年、Amkor Technology, Inc. All rights reserved.