# チップスケールのパワートランジスタパッケージング

著者: Shaun Bowers, VP, Mainstream Advanced Package Integration, Amkor Technology, Inc

アドバンストパワーパッケージング用のアプリケーションの拡大により、既存のディスクリート設計とパワーモジュール設計の間のギャップを埋めるための新しいパッケージ設計コンセプトの必要性が生まれました。集積型パワー半導体パッケージは、高度なパワー半導体技術の確立と共に、拡大と進化を続けています。現在の環境を理解し、前進するための課題を理解することは、新たなパワーパッケージング技術を取り入れるために必要なことです。

#### 進化するパワーエレクトロニクス市場

通信、データセンター、電気自動車、ハイブリッド電気自動車、ワイヤレス電力は、現在の先進パワーエレクトロニクス設計を推進するアプリケーションの一つです。世界のデータセンターのパワー市場だけでも、2019年から 2025年までに年率 12%の平均成長率で成長し、2025年には約 10億ドルに達すると予測されています[1]。ただし、すべての電子製品には DC-DC 変換、DC-AC 変換、簡易電源スイッチが必要です。今日の設計でパワーエレクトロニクスを改善するためには次のようなことが必要です。

- 抵抗値/インダクタンスの低減

- 集積型コントローラ/ロジック/パッシブコンポーネント

- フォームファクタの縮小

電源回路の低スイッチング損失を実現するためには、低オン抵抗(RDS(オン))および低インダクタンス (LDS)が必要です。これら設計細部に注意を払わなければ、パッケージはさらに大きな電力損失を処理しなければならないか、またはその電力能力が制限されているため、より低い電力アプリケーションに対応しなければなりません。多数の電力制御集積回路(IC)が利用できるようになり、コントローラの集積化が一般的になってきました。どのようなエンドデザインでも利用可能なスペースは常に限られているため、フォームファクタの縮小が必須です。

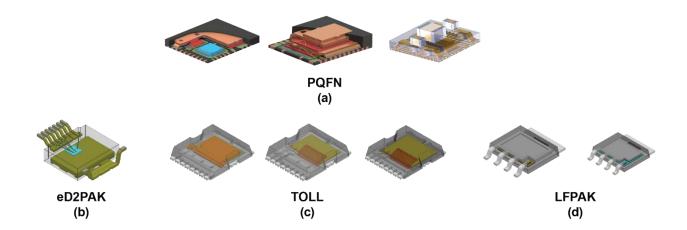

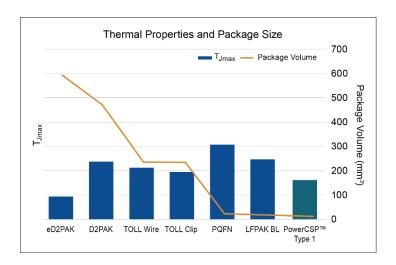

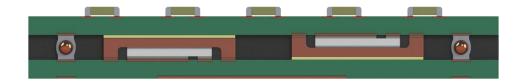

ますます厳しくなるシステム設計に対応するために、パワーディスクリート・パッケージングは、スルーホールからリード付き表面実装デバイス(SMD)、リードレス SMD、両面冷却 SMD、チップスケールの金属酸化物半導体電界効果トランジスタ(MOSFET)へと進化してきました。これらの要件に対応する現在の選択肢には、PQFN(Power Quad Flat No-Lead)、eD2PAK(Exposed Double-Decawatt Package)、TOLL(To-leadless package)、および LFPAK(Loss-Free Package )など多数のディスクリートソリューションがあります。 $\mathbf{図1}$ は、既存のディスクリートパワーパッケージングの例と、PQFN パッケージングの進化を示しています。 $\mathbf{表1}$ は、これらのパッケージのさまざまな特性を比較したものです。

図 1: 現在利用可能なパワーディスクリート機能には、a)PQFN、b)ヒートスプレッダータブ付き eD2PAK 、c)TOLL バリエーション、および d)LFPAK があります

| Pkg Type  | Pkg Size (mm) |      |      | mm²    |                          |

|-----------|---------------|------|------|--------|--------------------------|

|           | x             | у    | h    | Area   | Total Copper<br>Volume % |

| eD2PAK    | 14            | 11.7 | 3.6  | 163.8  | 28.96%                   |

| D2PAK     | 10            | 10.5 | 4.45 | 105    | 23.24%                   |

| TOLL Wire | 9.9           | 10.4 | 2.3  | 102.96 | 17.23%                   |

| TOLL Clip | 9.9           | 10.4 | 2.3  | 102.96 | 20.10%                   |

| PQFN      | 5             | 6    | 0.83 | 30     | 13.65%                   |

| LFPAK-BL  | 4.9           | 4    | 1.05 | 19.6   | 32.07%                   |

表 1: 既存のパワーパッケージの比較データ

炭化ケイ素(SiC)や窒化ガリウム(GaN)などのワイドバンドギャップ(WBG)半導体技術は、シリコン MOSFET と比較して高い性能指数(FOM)を有しており、パワーエレクトロニクスの効率、出力電力および スイッチング周波数範囲、動作温度範囲を拡大してきました。それと同時に、パワーパッケージに新たな課題 とチャンスを生み出しました。

より低い損失で、より高い電力負荷を制御することができるパワーデバイスもあります。例えば、GaN パワートランジスタを使用すると、パワーシステムはシリコンベースのシステムと比較して、サイズ、重量、およ

び効率損失を 1/4 にすることができます。GaN 技術は、低電力(50W)から中電力、さらには高電力レベルまで、ワイヤレスシステムなどでシステムの課題を解決することができます。5G アプリケーションで採用されているため、高度な低消費電力から中消費電力のパッケージングに適しています。同様に、SiC は Si MOSFET のそれを超える電力制御能力を有しており、多くのアプリケーションで高度なパッケージングが必要とされています。WBG デバイスを活用するに、電力システム全体の価値を最大化するための新たなパッケージングオプションを必要とします。

業界標準は、SiC/GaN パワー技術の採用を加速することのできる継続的な開発に含まれます。これは、2017年に開始した JEDEC 半導体技術協会の JC-70 委員会の重点取り組みです。電力変換アプリケーションにおける GaN 素子の固有のロバスト性を保証するために JEP180 が最近刊行した「窒化ガリウム電力変換素子のスイッチング信頼性評価手順のガイドライン[2]」の影響で、革新的なパッケージングへの関心が高まるはずです。車載製品関連組織との JC-70 の持続的な協議も進行中です。

同様に、JC-70.2 分科会では、SiC パワーデバイスの試験と信頼性に関するガイドラインを提示しています。 どちらの取り組みも、特にパッケージングの進歩が半導体の性能と一致している場合には、これらの高度半導体技術の採用を奨励し、簡素化することが推奨されます。

#### 現在のパッケージング技術のギャップ

今日のディスクリートパワーパッケージは、クリップ、ワイヤ、はんだのインターフェイスの電気的性能に制限があります。一般的に、ディスクリートパッケージは、サイズや容積が大きくなると、より高いパワー処理能力が得られます。しかしながら、より効率的なトランジスタ技術(GaN や SiC など)は、同じサイズのパッケージでより多くの電力を処理したり、フォームファクタを大幅に縮小することが可能です。

PQFN は、同一パッケージ内にパワーMOSFET をスタックまたはサイドバイサイドで配置する複数チップ搭載に対応しています。プリント回路基板(PCB)のスペースをさらに削減し、電気効率を向上させるために、インダクタやパッシブデバイスをパッケージ内またはパッケージの上部に集積化することができます。

ディスクリートパワーパッケージングや PQFN が常に直面する課題は、アプリケーションに必要な電力を処理するパッケージサイズと、放熱に対応するための適切なインターフェイスを効果的に集積化することの難しさです。大型フォームファクタ(LFF: Large Form Factor)の PQFN は、パッシブ集積化のために露出したパッドを搭載することができますが、リードフレームの I/O 密度と Cu 厚に制約があります。LFF PQFN は、熱容量のトレードオフと、多くのダイアタッチ段階のプロセスの複雑さを増やすことにより、その機能を実現します。

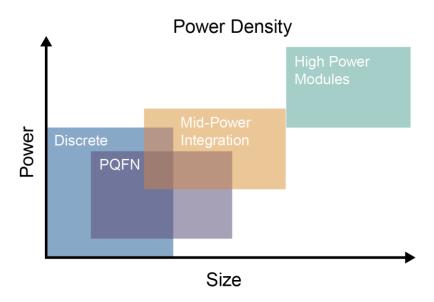

数百、数千ワットも扱うアプリケーションで最高の電力要件を満たすために、電力はパワーモジュールにパッケージされ、パッケージ寸法はミリメートルからセンチメートルにシフトしています。これらのパッケージは、通常、大型のヒートシンクにボルトやナットで取り付けられており、電気的な接続は、大型の電線やケーブルをネジで取り付けて行われています。図2に示すように、これにより、ディスクリートデバイスや大型パワーモジュールでは埋められない低電力から中電力の範囲にギャップが生じます。このギャップに、イノベーションと最適化が必要となります。

図 2: 低電力から中電力範囲のパワーアプリケーションは、ディスクリートと PQFN のスペースを重複させた 革新的な集積型パワーパッケージングの機会を提供します

エンベデッド技術でギャップを埋めようとするこれまでの試みでは、歩留まりの問題が伴う非常に複雑な設計になっていましたが、特定のアプリケーションの二ーズには対応していました。多くは技術的に対応可能でしたが、顧客がターゲットとする二ッチな市場に対応するためには、その採用は限られたものになっています。サプライチェーンのほとんどが基板メーカーを通じてのものになっているため、歩留まりとコストの責任の所有が、メインストリームのパワーパッケージング技術へ移行するの妨げになっていました。

最終的には、損失の大きいインターフェイスを排除して電力からパッケージへの密度を高める必要性から、低電力から中電力アプリケーション向けの新たな集積型パワーパッケージングのコンセプトが誕生する機会が生まれました。

### PowerCSP™設計コンセプト紹介

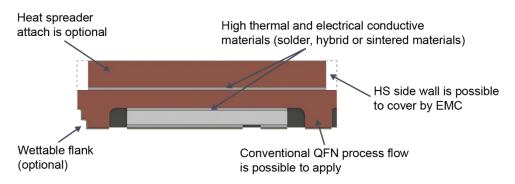

この集積型電力スペースの機能を抜本的に向上させるためには、3 つのことが必要です。まず、ソースとドレインからの導電率を最大にする必要があります。第二に、熱的および電気的インターフェイスを排除するか、 長さや厚さを大幅に縮小する必要があります。第三に、パッケージの導電性材料の密度を高める必要がありま す。PowerCSP™(PCSP) テクノロジーは、パワーアプリケーション用のチップスケールのパッケージ (CSP) を再考または再開発することで、これら 3 つの目的をすべて達成すると同時に、デバイスの全体サイズを縮小します。図3は、ヒートスプレッダー(HS)やその他のオプションを含む、このパッケージ設計の重要な面を示しています。

図3: PowerCSP™ テクノロジーの実装は、その柔軟性と多くの構築オプションを示しています

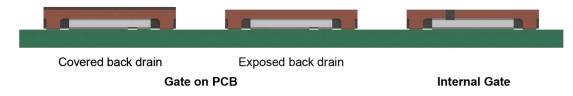

従来のパワーパッケージングにおける全体の導電性を最大化するためには、ソースとドレインは、チップ設計における利用可能なスペースの 100%またはそれに近い割合で通電材料に接続される必要があります。一般的には、ワイヤの数を増やしたり、ワイヤの直径を大きくしたり、またはソースまたはドレインに取り付けられたクリップの大きさを最大にすることによって行われます。PowerCSP テクノロジーでは、通電と放熱の両方の役割を果たす Cu パッドを介してチップを直接接続することで、チップが利用可能なすべてのソースおよびドレイン領域を使用できるように設計されています。図4は、接続オプションを示しています。

図 4: PowerCSP™ デザインは、チップスケールの電力に多くの接続オプションを提供します

パワーデバイスの各インターフェイスは、熱または電気スロットルとして機能することもあるため、過酷な環境下では故障の原因となる可能性があります。そのため、デバイスとシステムのインターフェイスは少ないほど良く、それらを排除して制御可能な電気経路を提供することがトレンドとなっています。PowerCSP 技術は、チップから通電部材への単一接続へのインターフェースを最小限に抑え、ソースまたはドレインのいずれかを PCB または他の基板内の電源または信号に直接接続できるようにします。

熱的特性と電気的特性の両方を最大化するためには、パッケージの体積内に可能な限り多くの導電性材料を有することが好ましいです。今日のほとんどのパワーパッケージングでは、パッケージ内の導電性材料が 25%

を超えることはほとんどありません(**表 1**参照)が、弊社の新技術は 40~70%の範囲にあります。これは、クリップの代わりに連続した Cu 基板を使用したことによるものです。

市場の特定のニーズに対応するための特注パワーパッケージング設計は数多くありますが、広く採用するためには、現在使用されている縦型および横型の MOSFET 設計の多くに対応できる柔軟な設計が必要です。

PowerCSP のバリエーションは、コア材のコンセプトを利用して、高電力密度を維持しながら個々のアプリケーションのニーズに対応することができます。ソースとゲートが露出しているデザインでも、パッケージ内部に配線されたゲートでも、新技術を使用したすべてのデザインで、高電力密度、高導電性材料密度、最小限のインターフェイスを実現しています。また、個々のデバイス性能の必要に応じて、追加のヒートシンク厚、片面または両面ドレイン設計、はんだ、焼結またはハイブリッド材料の使用などのバリエーションもあります。必要に応じて、ウェッタブルフランクのようなアプリケーション固有の機能強化も可能です。この新たなコンセプトのパッケージサイズは、個別のチップサイズに従い調整するか、または一般的な業界のフットプリントを使用することができます。図5は、いくつかの可能性のあるバリエーションを示しています。

図 5: PowerCSP™設計の柔軟性に基づくチップスケールパワーのパッケージバリエーション

Si、GaN、SiC のいずれの技術であっても、すべての半導体パワーデバイスにおける問題の1つは、動作温度の上昇です。車載製品は最も厳しい条件を要求され、エンジンルーム内ではパワーデバイスを175℃~200℃の温度で動作させなければならない場合もあります。パッケージングは、高温の課題に対処するために不可欠な要素です。

小型のフォームファクタを実現するにあたり、PowerCSP 設計のトレードオフの1つは、横方向のパッケージ内の銅の量が限られていることです。新技術では、チップ上に厚いリードフレームを使用しているにもかかわらず、小さいフォームファクタのためにパッケージの質量とサイズが大幅に削減されます。そのためには、積分熱容量を減少させ、一部のアプリケーションで許容可能な熱ソリューションを実現するために外部ヒートシンクを必要とします。図6は、パッケージが熱拡散を単独で担っている際にモデル化された様々なパッケージの相対的な接合部温度と質量を示しています。ヒートシンクが利用できるか、簡単に追加できる場合は、この制限は簡単に解決されます。

図 6: さまざまなパワーパッケージについての相対的な接合部温度 vs パッケージ体積

それぞれの設計バリエーションは、既存の高密度パワーデバイスを製造するための精密なプロセスを今でも活用しています。ワイヤーおよびクリップの必要性をなくすことで、従来のパワーパッケージングと比較して、製造フローのプロセスステップを簡素化することができます。PowerCSP設計では、フレームが電気クリップになっているため、製造工程では2~3のプロセスステップが削減されます。重要なプロセスステップは、ダイアタッチ、モールドおよびシンギュレーションですが、他のパッケージでは、ワイヤボンド、はんだ印刷、クリップ配置、追加のクリーニングステップなどの追加ステップがある可能性もあります。

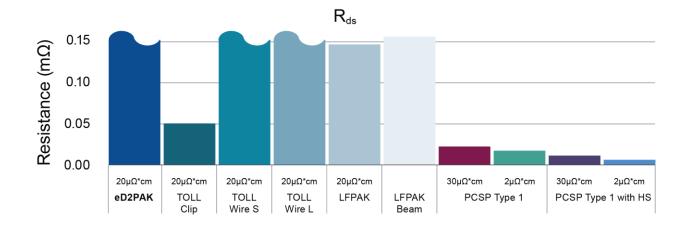

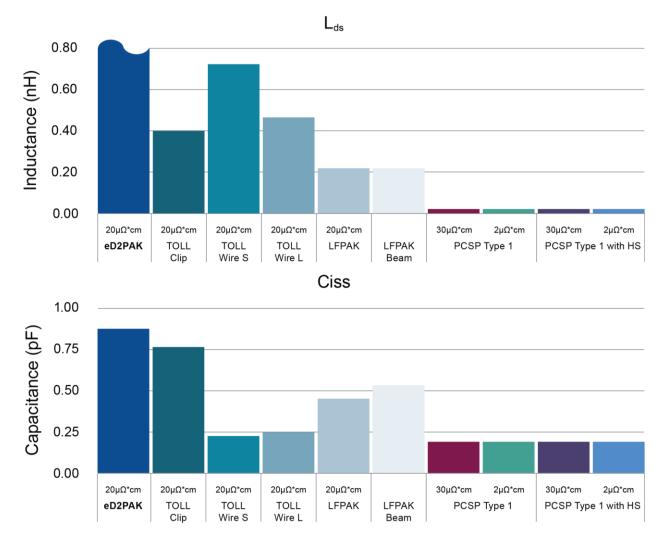

PowerCSP の設計では、他のディスクリートパッケージと比較して、低抵抗(R)、低インダクタンス(L)、大容量(C)性能が可能になります。**図7は**、他のディスクリートパワーパッケージ(**図1**参照)に対するパッケージのモデル化された RLC を示しており、チップから本体への接続のために様々なインターフェイス材料が使用されています。

図 7: PowerCSP™(PCSP)設計用の RDS、LDS、Ciss と様々なバージョンの eD2PAK、TOLL、LFPAK パッケージとの比較シミュレーション

導電性材料の密度が非常に高いパッケージでは、高い性能が得られます。同じ理由でインダクタンスが低く、 静電容量も他のパッケージに比べて若干低くなります。RLC の性能は、基本的には熱的にも最大電流を流すことにもメリットがありますが、ダイアタッチ材料の導電性や新設計自体の厚さに大きく依存していることはないようです。ワイヤを使用したデバイスと比較して、損失密度は非常に低いです。電気シミュレーションにより、小型パッケージと大型パッケージの両方と比較して、設計の性能を検証しました。

# PowerCSP のコンセプトを使用した低電力から中電力の集積化

パワー半導体では集積化に向けた強い動きがあり、様々な方法で電力密度が大きな役割を果たしています。低 消費電力から中消費電力の範囲では、集積化は使用ケースや元のパッケージ形式に応じて様々な方法で行われ る可能性があります。 集積化には、3 つの基本的なアプローチがあります。1 つは、コントローラと MOSFET デバイスを単純にスプリットパッドリードフレームや PQFN に含める方法です。もう一つは、絶縁ゲートバイポーラトランジスタ (IGBT) モジュールで一般的なダイレクトボンド Cu (DBC) のような、より非標準的な材料をモールドインターフェイスに含める方法です。最後に、MOSFET のチップをラミネート基板や再分配層(R D L ) パッケージに直接エンベッドするという取り組みが行われています。エンベデッドのオプションは中電力オプションではメリットがありますが、サプライチェーンに課題があるため、完全なエンベデッドの普及は遅れています。これらの集積化の方法にはそれぞれ長所と短所がありますが、いくつかの共通の特徴があります。それらはみな FET のソースとドレインへの接触面積を最大化し、モジュール内に可能な限り多くの導電性材料を配置し、集積化を成功させるために電気経路を短縮して設計しようと試みています。

PowerCSP 技術を利用した集積化へのアプローチは、他のアプローチに内在する根本的な課題のいくつかを解決する可能性があります。共通のフォームファクタから始めて、このアプローチをよりメインストリームのモジュールアスペクトに集積化することで、より幅広い採用が可能になります。MOSFET を予めパッケージ化しておくことで、個別テストや集合テストが可能になるため、歩留まり向上のための KGD(Known Good Die)として取り扱うことができます。パッケージを基板や PCB に直接実装することで、全体的な複雑さやコストを削減できる可能性があります。

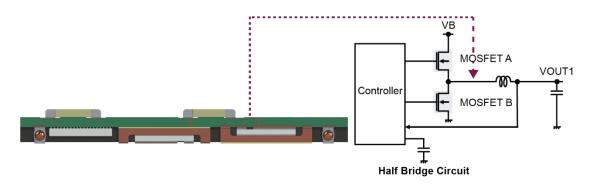

モジュール式アプローチでは、集積化されたデバイスのためのいくつかの特定の設計オプションにより、システム全体の性能を強化します。PCBへの直接の信号経路は、低抵抗/低インダクタンスを保持します。高密度でありながら小型フォームファクタのパッケージを使用することで、設計上もっとも重要となる領域にのみ厚いCuのインターフェイスを使用することができます。また、最重要となるコンポーネントやデバイスは、性能とコストについて距離を最適化することができます。このアプローチを典型的なハーフブリッジ回路に適用することで、設計の自由度のメリットがより明らかになります。ハーフブリッジ回路では、性能に大きく影響する設計上の最重要な要素の1つとして、MOSFETのソースから他のMOSFETのドレインおよびインダクタまでの距離が挙げられます。PowerCSP設計を使用することで、インダクタをMOSFET間に直接配置することができ、MOSFETとパッシブコンポーネント間のラインインダクタンスを最小限に抑えるために、距離を非常に短くして最適化することができます。図8はこのアプローチを示しています。

図8: PowerCSP™の方法論を使用した電力の集積化の増強

更なる集積化が必要な場合、または MOSFET の両側に配線が必要な場合、基板技術内に埋め込む技術の代替として使用できるシンプルなコンセプトがあります。図9では、2つの薄いラミネート構造体を用い、その間に MOSFET のモールド構造を挟んでいます。これらの設計とプロセスには十分な実績がありますが、電力アプリケーションではなく、モバイルアプリケーションで使用されています。シンプルさとプロセスの再利用は、その実績と商品化までの時間の早さから、将来的には重要な代替になる可能性があります。

図 9: PowerCSP™の方法論を使用した 電力の集積化の増強

#### 低電力~中電力の集積化イノベーション

車載製品、通信、データセンター、コンシューマー家電、その他の分野におけるパワーエレクトロニクスの新たなアプリケーションや、高度パワートランジスタ技術により、電力変換における既存のディスクリートパワーパッケージとパワーモジュールの間のギャップを埋める革新的なパワーパッケージのニーズが生まれました。

PowerCSP 設計は、高電力密度パッケージを可能にする MOSFET CSP を提供します。この機能は SiC や GaN トランジスタに適用可能で、集積化に向けた重要な構成要素となります。それは、チップのサイズや規格、大容量フォーマットに拡張可能な小型フォームファクタを使用しています。その設計は、様々なアプリケーションに対応できる柔軟性を持ち、コストを削減するために KGD(Known Good Die)と厚い Cu を必要な部分のみに使用し、アクティブ/パッシブエレメントへの電気経路を短縮して効率を高め、低ノイズ化を実現します。この設計アプローチについては、特許が申請されています。

スマートフォンのような低電力市場では、すでにウェハレベルの CSP MOSFET が実装されています。マザーボードやドーターボードへのパワートランジスタの直接実装はすでに行われており、高度チップスケールのパワーパッケージが利用できるようになると、需要が拡大する可能性があります。コンシューマー向けパワーエレクトロニクスにおける表面実装パッケージにおける例の通り、低電力アプリケーションにおける低ノイズパッケージの普及に続き、このパッケージはより高い電力領域にまで需要が拡大することが見込まれます。

垂直統合型デバイスメーカー(IDM)は、通常、パッケージングに関して独自の社内アプローチを持ち、特別な目的のために後工程受託企業(OSAT)を使用していますが、集積型パワーデバイスは、OSAT を選択する重要な目的の1つになる可能性があります。OSATによるサプライチェーン上のメリットに加え、弊社の製品には、小型化、冷却性(適切なヒートスプレッダを使用)、静音性、低コスト性といった新たな設計アプローチによる優位性もあります。これらのメリットを組み合わせることで、低抵抗/低インダクタンスパッケージの幅広い採用につながる可能性があります。

#### 謝辞

PowerCSP は Amkor Technology, Inc.の商標です。

# 参考資料

- 1. 「収益を生み出す世界のデータセンター電源市場規模」、Arizton Advisory & Intelligence レポート: https://www.openpr.com/news/2047478/global-data-center-power-market-size-to-generate-revenues

- 「窒化ガリウム電力変換素子のスイッチング信頼性評価手順のガイドライン」、JEP180、 https://www.jedec.org/standards-documents/docs/jep180

# バイオグラフィー

Amkor Technology, Inc. Mainstream Advanced Package Integration VP、Shaun Bowers。2000 年 Amkor 入社、現在は車載製品、リードフレーム、パワービジネスセグメントのパッケージ開発を担当。それ 以前は、技術プログラム管理、販売、顧客サービスなどの職務にも従事。Amkor 入社前、Johnson Matthey Electronics および Honeywell Electronic Materials に勤務。ゴンザガ大学機械工学学位取得。メール:shaun.bowers@amkor.com