### BENEFITS OF FLIP CHIP

- ▶ 信号インダクタンスの低減 チップと 基板の接続長さが非常に短く(0.1 mm vs 1~5 mm)、信号経路のインダクタ ンスが大幅に低減されます。これは高速 通信およびスイッチング機器に重要な 要素です。

- ▶ Power/Groundインダクタンスの低減 フリップチップ接続を使用することによりチップのコア部に直接電源を供給することができます。そのためチップ端からコア部への電源供給を配線で行うことを必要としません。これによりコア電源のノイズが大幅に低減され、デバイス性能が改善されます。

- ▶ より高い信号密度 チップ外周だけでなくチップの表面全体を接続に使用します。これはQFPとBGAパッケージの比較に似ています。フリップチップはチップの表面全体にわたり接続が可能であるため、同じサイズのチップでより多くの接続が可能です。

- ► チップのシュリンク パッドによりチップサイズが制限される場合(つまりボンディングパッドに必要なチップ外周のスペースによりチップサイズが決まる場合)、チップサイズを縮小し、デバイスのコストを低減します。

- ▶ パッケージのフットプリント低減 フリップチップを使用することにより、パッケージサイズを低減できるケースがあります。これはチップ端からパッケージ端の幅を減らすこと(ワイヤを張るための余分なスペースが不要になるため)、より高密度の基板を使用することによるパッケージピッチの低減により実現されます。

# Flip Chip Packaging

フリップチップ接続の需要は、半導体業界の多くの分野から、さまざまな要因によって高まりを見せています。この需要に応え、フリップチップ・イン・パッケージ(FCiP)技術のリーディングプロバイダーであり続けるため、Amkorは日々研鑽を重ねています。当社は、業界を牽引する様々なお客様と緊密なパートナーシップを築くことで、大規模なフリップチップパッケージとその組立をサブコン市場へもたらしました。1999年にFCiPを提供する業界初のOSATとなって以来、Amkorはフリップチップ接続を利用した革新的なパッケージングのソリューションを提案し続けてきており、今尚業界最大規模の幅広いFCiP技術のソリューションを提供しています。

## What Is Flip Chip?

フリップチップは、SOIC等のような特定のパッケージ名称ではなく、またBGA のようなパッケージの種類でもありません。フリップチップは、「チップをパッケージキャリアへ電気的に接続する方法」のひとつです。基板、リードフレームのいずれであっても、パッケージキャリアはチップをパッケージの外部へ接続する役割を持っています。"標準的な"パッケージでは、チップとキャリア間の接続はワイヤで行われます。そのようなパッケージでは、チップは表面を上にしてキャリアに搭載され、ワイヤはまずそのチップ上に接続されてからその後ループを張ってキャリア側に接続されます。ワイヤは一般的に長さ1~5 mm、直径15~35 μm程度です。

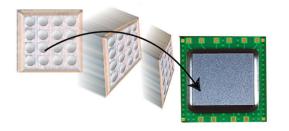

これとは異なりフリップチップパッケージでは、チップとキャリア間の接続はチップの表面に直接設置された導電性バンプによって行われます。バンプを搭載されたチップは裏返しにされ(フリップ・オーバーされ)、表面を下にして、バンプが直接キャリアに接続されます。バンプは一般的に高さ $60\sim100$   $\mu$ m、直径が $80\sim125$   $\mu$ m程度、Cuピラー(CuP)バンプの場合は一般的にSnAgでキャップされており高さは40  $\mu$ m程度です。

フリップチップ接続は一般的に、はんだもしくは導電性接着剤を使用して形成されます。最も一般的な接続方法ははんだ付けです。現在のはんだのオプションは、共晶Sn/Pbまたは鉛フリー(Sn: 98.2%、Ag: 1.8%)です。はんだバンプされたチップは、BGAのボールをパッケージ裏面へ取り付けるのと同じように、はんだリフローによって基板へ取り付けられます。チップがはんだ付けされた後、チップと基板の間にアンダーフィルが充填されます。

アンダーフィル樹脂は、チップとキャリア間に入り込みはんだバンプを取り囲むように充填するために特別に設計されたエポキシ樹脂です。さらにアンダーフィル樹脂は、チップとキャリア間の熱膨張の差によって生じるはんだ接合部の応力を制御するように設計されています。硬化後、アンダーフィルは応力を吸収し、はんだバンプ上の応力を減らし、パッケージの寿命を大幅に伸ばします。チップの接続とアンダーフィルの工程はフリップチップ接続の基礎となります。この工程以降、想定されるパッケージの組立方法には多くの選択肢があり、また一般的に使用されている製造プロセスやパッケージの形状を適用することができます。

更に新しいフリップチップ接続技術として導入が始まっているのがTCNCP(熱圧着非導電性ペースト)と呼ばれる方法です。これは、はんだ付け・アンダーフィルというプロセスではなく、その両方を単一の工程で行います。先端をはんだ付けしたCuピラーバンプは液体のエポキシアンダーフィルの中に押し込まれ、次に双方に熱がかけられて金属結合を形成し、エポキシを硬化させます。TCNCPとCuピラーの使用により、チップとキャリアの間のスタンドオフが維持されてショートの問題が回避されるため、より微細なバンプピッチの適用が可能になります。

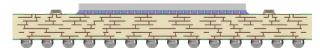

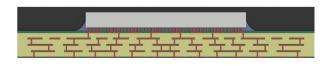

Bare die FCBGA cross section

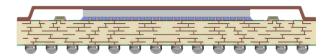

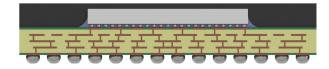

Single piece lid FCBGA cross section

# Wafer Bumping Technology

Amkorは、フリップチップ組立をサポートするため、韓国、台湾、ポルトガルおよび中国の製造拠点にウェハバンピングラインを設置しました。Amkorのバンピングは、市場において最も先進的でロバスト性があり、信頼性が高く、また高歩留まりを実現する、当社独自の電気めっきはんだ技術に基いています。共晶Sn/Pb、Pbフリー(Sn:98.2%、Ag: 1.8%)およびCuピラーのすべてのバンピングが200 mmと300 mmのウェハで量産されています。

- ▶ ウェハサイズ: 200 mm、300 mm

- ► フルエリアアレイピッチ:130 µm ペリフェラルパッドピッチ:100 µm未満

- ▶ Cuピラー、共晶Sn/Pbおよび Pbフリー(Sn98.2/Aq1.8)対応

- ▶ 低アルファ (<0.02 cph) および 超低アルファ (<0.002 cph) はんだ使用可</p>

- ▶ ポリイミドリパッシベーション使用可

- ▶ Cuめっきを使用した再配線対応

## Packaging Options Using Flip Chip

半導体パッケージには、チップとアプリケーションの要件に応じて、様々なパッケージレベルのソリューションが要求されます。フリップチップ接続は、それぞれの市場においてメリットを持つ幅広いパッケージソリューションへ適用することができます。Amkorはお客様とエンドユーザーの多様なニーズに応えるため可能な限り広範なフリップチップパッケージングソリューションを提供します。製造に関する幅広い知見を、あらゆるタイプのパッケージングインターポーザと組み合わせ、さらにフリップチップ接続技術のリーディグカンパニーであることを活かし、Amkorは最新のパッケージソリューションを追求し続けます。

## Flip Chip BGA Package

AmkorのFCBGAパッケージはラミネート基板またはセラミック基板を用いて組み立てられます。複数の高密度配線層、レーザードリル加工のブラインドビア、埋め込みビア、スタックビア、超ファインライン/スペースメタライゼーションを利用したFCBGA基板は、極めて高密度の配線を備えています。フリップチップ接続と超高度な基板技術を組み合わせることにより、FCBGAパッケージは電気性能を最大限に引き出すように電気的にチューニングが可能です。電気的性能が確定されると、フリップチップにより可能となるデザインの柔軟性により最終的なパッケージデザインにおけるオプションが広がります。幅広い最終アプリケーションの要件を満たすため、Amkorはさまざまな種類のFCBGAパッケージを提供します。

FCBGAは幅広い選択肢を備えており、最終製品の熱特性ニーズに合致するようにカスタマイズされたパッケージの選択が可能です。高性能ASICの多くは、放熱性樹脂を用いてCuヒートスプレッダーに直接チップを接着するリッド搭載タイプを採用します。これにより、パッケージと外部の放熱部品との間で極めて低い熱抵抗(Theta JC)が得られます。Cuヒートスプレッダーはチップからパッケージ周囲、そしてマザーボードへと、熱を平面方向へ効率的に拡散します。

低ワット数の製品は一般的にベアチップまたはモールドタイプを使用します。これらのケースでは、はんだバンプとコアビアを持つフリップチップ接続はチップの通電側から基板までの抵抗パスが低くなり、パッケージ表面からとマザーボード内の両方への放熱を可能にします。

このICパッケージング技術は、多ピン製品やハイパフォーマンスASICに最適です。大型FCBGAはインターネット、ワークステーションプロセッサおよび高帯域幅の通信機器に対してパッケージングソリューションを提供します。フリップチップ接続を用いることにより、旧来の表面実装パッケージと同サイズで数千ものPad接続を実現します。FCBGAはまた、ゲーム機器のプロセッサやグラフィックス、最先端のポータブル機器向けのハイエンドアプリケーションプロセッサに最適なパッケージでもあります。

### **Package Options**

- ▶ ウェハノード ≥7 nm 認証済 (5 nm開発中)

- ▶ 基板表面及び裏面にSMTコンポーネンツを実装可能

- ▶ マルチチップ対応

- ▶ パッケージ上部へのメモリ部品搭載

- ▶ リッド材料オプション

- ▶ グラウンデッド リッド対応

- ▶ カスタムBGA外形対応

## Flip Chip BGA Package (Cont.)

## **Technology**

- ▶ 基板

- ▶ 4~18層ビルドアップ基板

- ▶ 高CTEセラミック

- ▶ コアレス

- ▶ バンプタイプ

- ▶ Sn/Pb共晶

- ▶ Pbフリー

- ▶ Cuピラー (エリアアレイ、ファインピッチ ペリフェラル)

- ▶ パッケージフォーマット

- ▶ ベアチップ

- ▶ リッド搭載

- ▶ 成形

- アレイ配置バンプ: Minimum 90 μmピッチ

- ペリフェラル配置バンプ: Minimum 100 μmピッチ

- ▶ チップサイズ: 29 mm (Max)

- ▶ パッケージサイズ: 10 mm~66 mm (85 mm 開発中)

- ▶ BGAフットプリント: 0.4 mm、0.5 mm、0.65 mm、0.8 mm、1.0 mmピッチ

FCBGA/LGA (Bare die)

グラフィクス、PCチップセット、ローエンドASICアプリケーション向けフリップチップパッケージングソリューション

fcCeramic CBGA/CLGA/CLLGA/solder column interposer

フリップチップ接続をしたパッケージングとしてはオリジ ナルの形態

## Flip Chip CSP Package

#### **Features**

- ▶ 高周波アプリケーション向け設計

- ▶ ターゲット市場:携帯電話、その他の携帯機器

- ▶ 薄型コアラミネートまたはセラミックパッケージ

- ハンドリングとセカンドレベル信頼性を考慮したオーバーモールド設計

- ▶ パッケージサイズ: 3 mm~15 mm

- ▶ バンプピッチ ペリフェラルアレイ: Minimum 150 µmエリアアレイ: Minimum 250 µm

- ▶ 0.5~1.0 mm BGAもしくはLGAボールピッチ

- Minimumパッケージ厚 LGA: 0.80 mm、 0.5 mmピッチBGA: 1.0 mm、 0.8 mmピッチBGA: 1.2 mm

**fcCSP**

CSPパッケージ向けフリップチップソリューション

# Flip Chip System in Package (SiP)

フリップチップSiPパッケージは、接続技術に旧来のワイヤボンドではなくフリップチップを用いたAmkorのSiPパッケージです。このパッケージには、通常のはんだバンプもしくははんだコーティングCuピラーバンプを形成したシリコンもしくはGaAs(またはその両方)と、複数の受動部品が混載され、2層または4層の基板が使用されています。このパッケージ構造は、サイズ、パフォーマンスおよびコストの面から、RF電源アンプおよびRFフロントエンドモジュールアプリケーションで支持されています。

バンプ高さのコントロールにより接続インピーダンスが制御され、製品の性能が安定します。Cuピラー上のウェットティップのハンダ量を少なくすることで、チップ下のソルダーマスクをなくすことができるようになります。これにより基板の複雑さやコストを削減し、なおかつRFアプリケーションに必要な極少ピッチのFC接続の壁を取り除くことができます。フリップチップ接続によりウェハのバックグラインディングが不要になる場合もあり(モールドキャップ厚0.9 mmの場合)、更なるコスト削減とプロセスフローの簡素化に貢献します。

## Flip Chip SiP (Cont.)

RFアプリケーション向けのパッケージは少~中程度のI/O数があり、サイズは極めて小さいです。チップ下のはんだマスクが不要になりスタンドオフを大きくすることから、トランスファーモールドを適用できる可能性が高まっています。このようにプロセスフローからアンダーフィル作業を無くすことができるため、大幅なコスト低減につながります。研究によりトランスファーモールドを用いたパッケージはMSLはもちろんHAST nadono加速試験において、アンダーフィルタイプのパッケージより、チップ内部応力のバランスやハンダとのCTEマッチングがよいことから、より信頼性が高いと考えられています。

Copper pillar or solder bump for GaAs and Si applications in LGA or BGA format

## Wafer Level Packaging - CSPnl

CSP<sup>n</sup>はセカンドレベルのボードの信頼性を改善したウェハレベルパッケージであり、パッドをJEDEC標準ピッチに配線するために薄膜再配線プロセスを利用しています。標準の「CSP」はんだバンプは再配線されたパッド上で形成されます。CSP<sup>n</sup>は標準的な表面実装とリフローの技術を利用できる様に設計されています。標準的な表面実装設備を使用し、アンダーフィルを不要とすることで、他のJEDEC規格のエリアアレイパッケージと同様のコストメリットを提供します。

#### **Features**

- ▶ 標準のJEDECピッチとCSPはんだボール径に対応

- ▶ 標準のSMT実装とテストに対応

- ▶ コスト効率の良い薄膜再配線技術を利用

- ▶ 裏面レーザーマーク対応

- ▶ 多くのアプリケーションにおいてアンダーフィル不要

- ► テストおよびテープ&リールを含むフルターンキー CSP<sup>®</sup>プロセス

- 共晶鉛フリーはんだボール

- ポリイミドリパッシベーション対応

- 認証済み、量産中

- ▶ 高信頼性:落下、曲げおよびキーパンチを含むすべてのハンドセット機械信頼性試験をクリア

詳細については<u>amkor.com</u>にアクセスしていただくか、または<u>sales@amkor.com</u> までメールをお送りください。

本文書中の情報に関して、Amkorはそれが正確であることまたは係る情報の利用が第三者の知的権利を侵害しないことについて、如何なる保証も致しません。Amkorは同情報の利用もしくはそれに対する信頼から生じた如何なる性質の損失または損害についても責任を負わないものとし、また本文書によって如何なる特許またはその他のライセンスも許諾致しません。本文書は、如何なる形でも販売の標準契約条件の規定を超え、如何なる製品に対しても、Amkorの保証を拡張させ、または変更することはありません。Amkorは通知することなくいつでもその製品および仕様に変更を行う権利を留保します。Amkorの名前と口ゴはAmkor Technology, Inc.の登録商標です。記載されている他の全ての商標はそれぞれの会社の財産です。⑥ 2021 Amkor Technology, Incorporated. All Rights Reserved. TS102P-JP Rev Date: 02/21